# High-Level Synthesis BLUE BOOK

MICHAEL FINGEROFF

# **High-Level Synthesis**

**Blue Book**

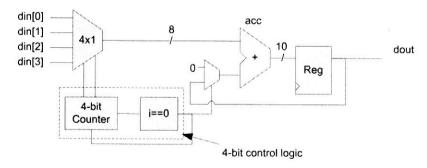

**Michael Fingeroff**

Copyright © 2010 by Mentor Graphics Corporation.

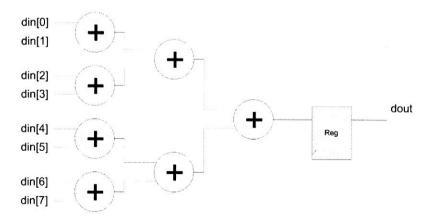

Library of Congress Control Number: 2010906504

ISBN: Hardcover 978-1-4500-9724-6

Softcover 978-1-4500-9723-9 E-book 978-1-4500-9725-3

All rights reserved. No part of this book may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying, recording, or by any information storage and retrieval system, without permission in writing from the copyright owner.

While the publisher and author have used their best efforts in preparing this book, they make no representations or warranties with respect to the accuracy or completeness of the contents of this book, and specifically (i) disclaim any implied warranties of merchantability or fitness for any specific purpose, and (ii) assume no responsibility or liability for the contents of this book or its use. No warranty may be created or extended by a sales representative or by written sales materials. The publisher and author caution that the advice and strategies contained herein may not be suitable for your situation. Neither the publisher nor author shall be liable for any loss of profit or any other commercial damages, including, but not limited to, special damages, incidental damages, consequential damages, or other damages arising directly or indirectly from the use of this book or the information contained herein.

This book was printed in the United States of America.

#### To order additional copies of this book, contact:

Xlibris Corporation 1-888-795-4274 www.Xlibris.com Orders@Xlibris.com

## **CONTENTS**

| Preface                                                              | 13             |

|----------------------------------------------------------------------|----------------|

| Who Should Read This Book                                            | 14             |

| About the Authors                                                    | 15             |

| Acknowledgements                                                     | 17             |

| Chapter 1                                                            |                |

| Making the Case for High-Level Synthesis                             | 19             |

| A broken design flow                                                 | 19             |

| Keeping up with the pace                                             | 20             |

| Benefits of high-level synthesis                                     | 20             |

| Reducing design and verification efforts                             | 21             |

| More effective reuse                                                 | 21             |

| Investing R&D resources where it really matters                      | 22             |

| Seizing the opportunity                                              | 22             |

| Chapter 2                                                            |                |

| General C++ Style                                                    | 25             |

| Introduction                                                         | 25             |

| File Organization                                                    | 25             |

| Building an Executable Using Makefiles                               | 26             |

| Makefile Naming                                                      | 26             |

| Comments                                                             | 26             |

| Macros                                                               | 26             |

| Targets                                                              | 26             |

| Phony Targets                                                        | 27             |

|                                                                      |                |

| Simple Makefile Example                                              | 27             |

| Simple Makefile Example                                              |                |

|                                                                      | 28             |

| Header/Include Files                                                 | 28<br>30       |

| Header/Include Files                                                 | 28<br>30       |

| Header/Include Files Test Benches Creating a Golden Reference Design | 28<br>30<br>30 |

| Chapter 3  Bit A courate Data Tunes                   |   |

|-------------------------------------------------------|---|

| Bit Accurate Data Types                               |   |

| Introduction 35                                       |   |

| Compilation, Debug, and Simulation Speed              |   |

| Header Files and Typedefs                             | 1 |

| Integer Data Types                                    |   |

| Unsigned integer                                      |   |

| Signed Integer                                        |   |

| Fixed Point Data Types                                |   |

| Unsigned Fixed Point                                  |   |

| Signed Fixed Point                                    |   |

| Quantization and Overflow                             |   |

| Truncation and Rounding                               |   |

| Saturation and Overflow                               |   |

| Operators                                             |   |

| Bitwise Arithmetic Operators: *, +, -, /, &,  , ^,%48 | 1 |

| Bit Select Operator: []49                             | 1 |

| Shift Operators: <<, >>50                             | ı |

| Shift Right Operator: >>50                            | 1 |

| Unsigned Shift Right50                                | 1 |

| Signed Shift Right50                                  | 1 |

| Shift Left Operator: <<51                             | 1 |

| Unsigned Shift Left51                                 | ı |

| Signed Shift Left                                     | 1 |

| Unexpected Loss of Precision                          | l |

| Methods54                                             | 1 |

| Slice Read: slc                                       | l |

| Problems with Compilation of Read Slice Method54      | ı |

| Slice Write: set_slc55                                | 1 |

| Explicit Conversion Functions55                       | 1 |

| Implicit Conversion Functions56                       | ı |

| Helper/Utility Functions56                            | ı |

| Array Uninitialization: ac::init_array56              | ı |

| ceil, floor, and nbits57                              | 1 |

| Complex Data Types                                    |   |

| Chapter 4                                             |   |

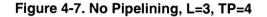

| Fundamentals of High Level Synthesis59                | ı |

| Introduction                                          | 1 |

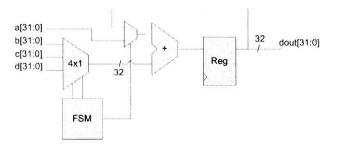

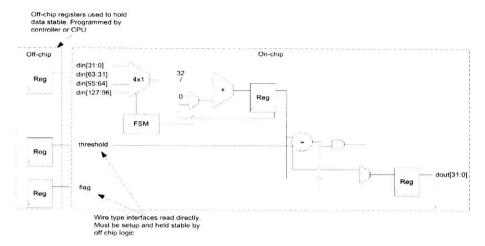

| The | Top-level Design Module                              | 39   |

|-----|------------------------------------------------------|------|

|     | Registered Outputs                                   | 60   |

|     | Control Ports                                        | 61   |

|     | Port Width                                           | 61   |

|     | Port Direction                                       | 61   |

|     | Input ports                                          | 61   |

|     | Output ports                                         | 61   |

|     | Inout Ports                                          |      |

| Hig | h-level C++ Synthesis                                | 62   |

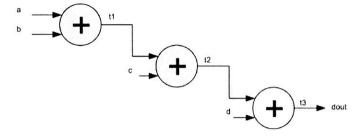

| Č   | Data Flow Graph Analysis                             | 62   |

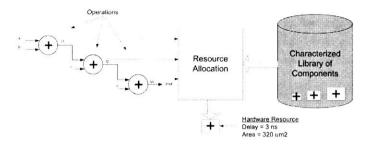

|     | Resource Allocation                                  | 63   |

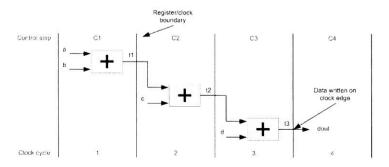

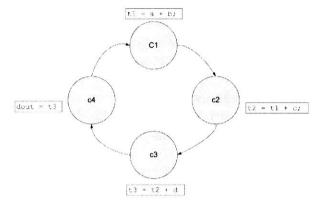

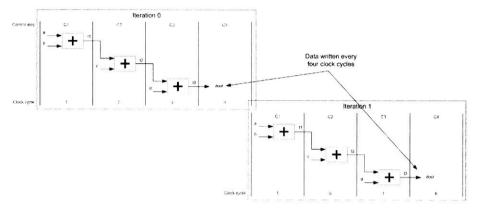

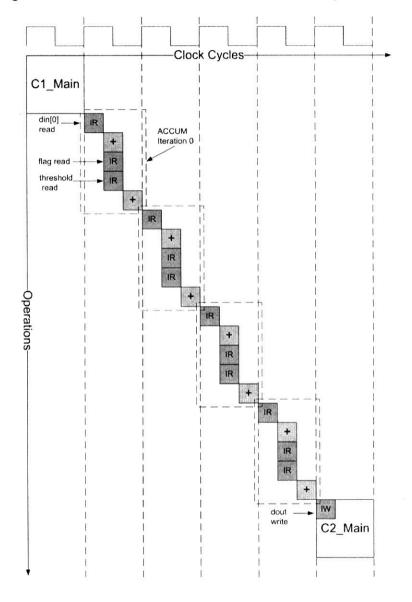

|     | Scheduling                                           | 64   |

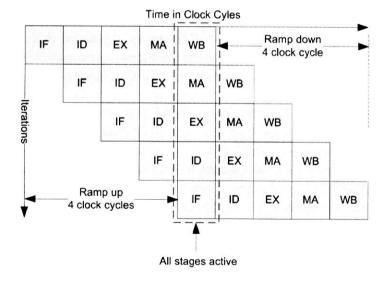

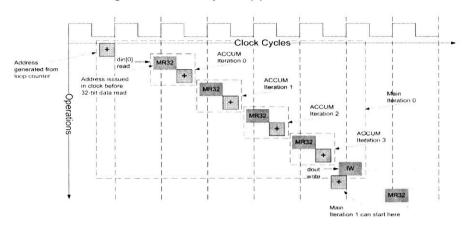

|     | Classic RISC Pipelining                              |      |

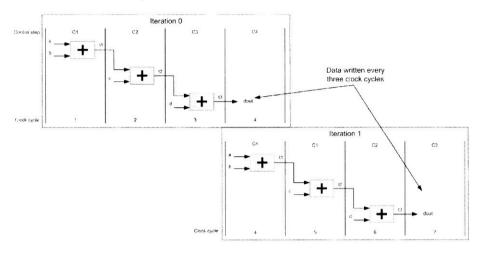

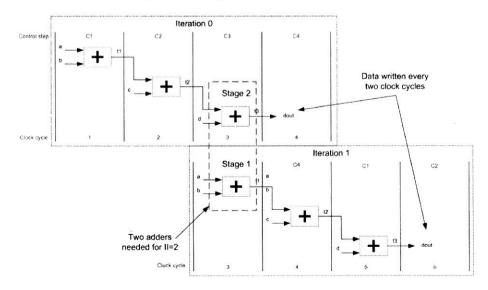

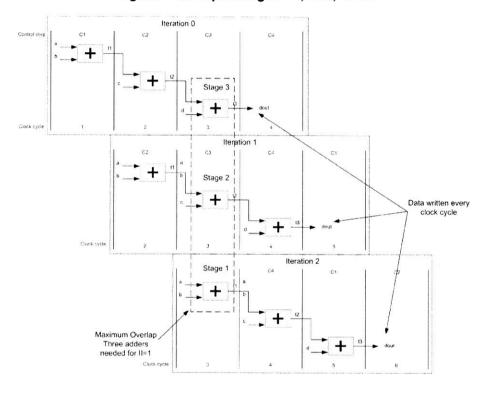

|     | Loop Pipelining                                      |      |

| _00 | ps                                                   |      |

|     | What's in a Loop?                                    |      |

|     | "for" Loop                                           |      |

|     | "while" Loop                                         |      |

|     | "do" Loop                                            |      |

|     | Rolled Loops                                         |      |

|     | Loop Unrolling                                       |      |

|     | Partial Loop Unrolling                               |      |

|     | Fully Unrolled Loops                                 |      |

|     | Dependencies Between Loop Iterations                 |      |

|     | Loops with Constant Bounds                           |      |

|     | Loops with Conditional Bounds                        |      |

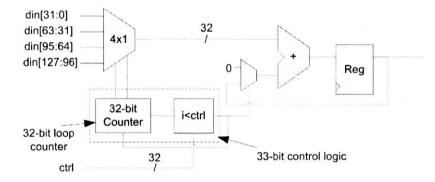

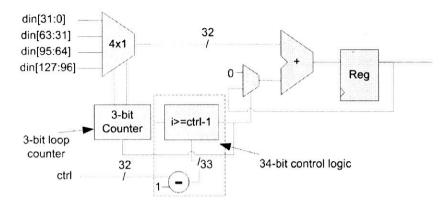

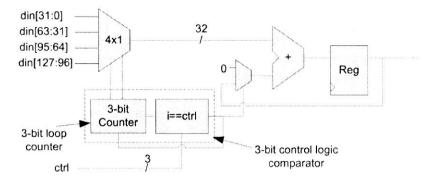

|     | Optimizing the Loop Counter                          |      |

|     | Optimizing the Loop Control                          |      |

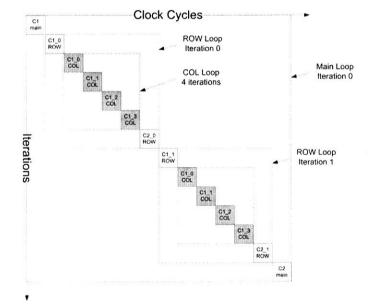

|     | Nested Loops                                         |      |

|     | Unconstrained Nested Loops                           | . 86 |

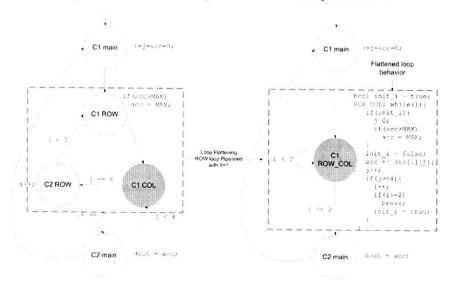

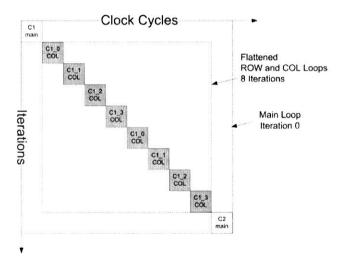

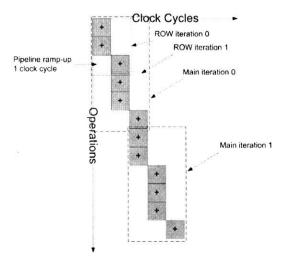

|     | Pipelined Nested Loops                               | . 88 |

|     | Pipelined ROW Loop With II=1                         | . 88 |

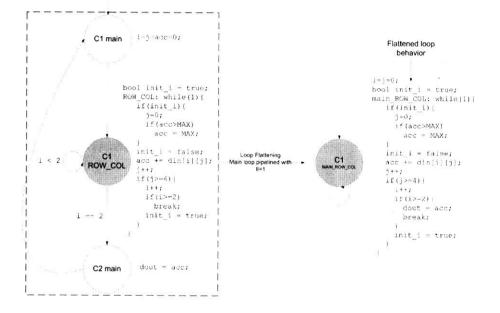

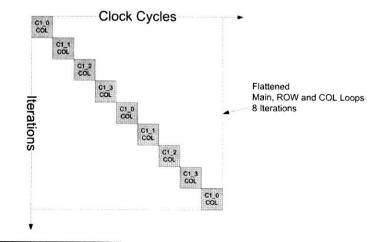

|     | Pipelined main Loop with II=1                        | . 89 |

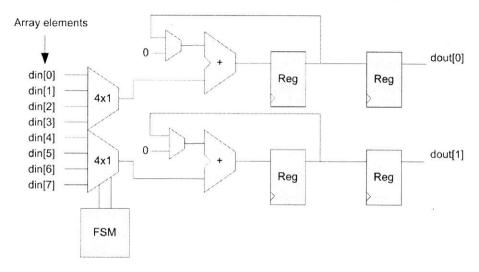

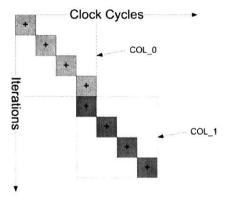

|     | Unrolling Nested Loops                               |      |

|     | Unrolling the Innermost Loop                         | .9   |

|     | Rampup/Rampdown of Pipelined Nested Loops            |      |

|     | Rampup Only of Nested Loops with Pipelined Main Loop |      |

|     | Unrolling the Outer Loop                             |      |

|     | Reversing the Loop Order                             |      |

|     | 1                                                    |      |

| Sequential Loops100                                         |

|-------------------------------------------------------------|

| Simple Independent Sequential Loops100                      |

| Effects of Unmerged Sequential Loops102                     |

| Manual merging of sequential loops104                       |

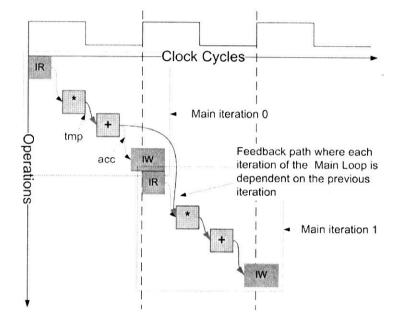

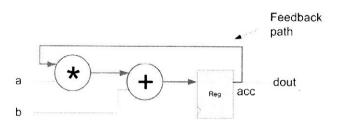

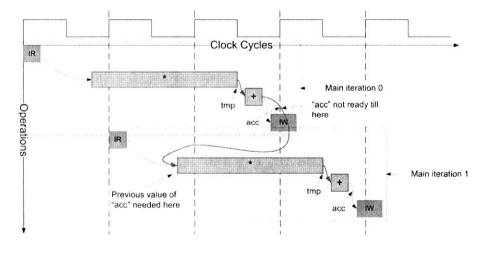

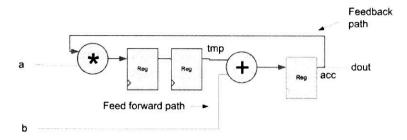

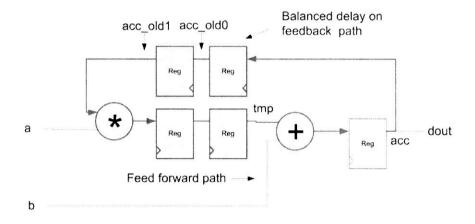

| Pipeline Feedback                                           |

| Data Feedback                                               |

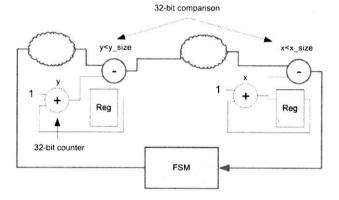

| Control Feedback109                                         |

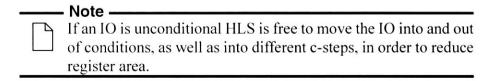

| Conditions111                                               |

| Sharing111                                                  |

| if-else statement                                           |

| switch statement112                                         |

| Keep it Simple112                                           |

| Functions and Multiple Conditional Returns115               |

| Replacing Conditional Returns with Flags116                 |

| References117                                               |

|                                                             |

| Chapter 5                                                   |

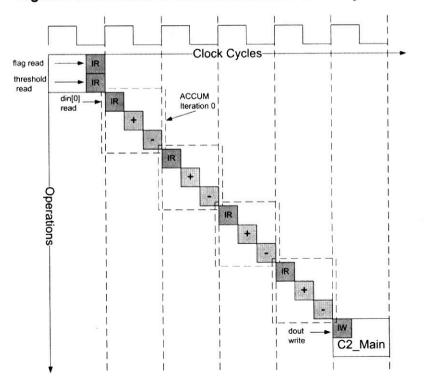

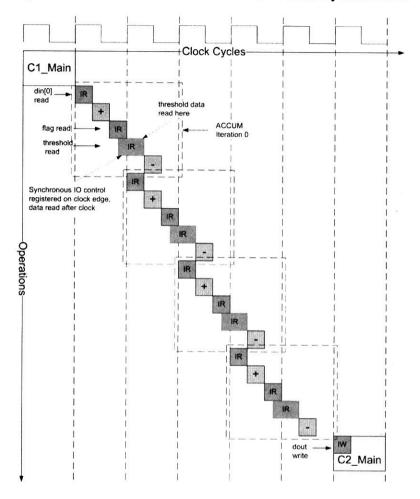

| Scheduling of IO and Memories119                            |

| Introduction119                                             |

| Unconditional IO119                                         |

| Pass by Reference                                           |

| Pass by Value122                                            |

| Conditional IO124                                           |

| Pass by Reference                                           |

| Pass by Value127                                            |

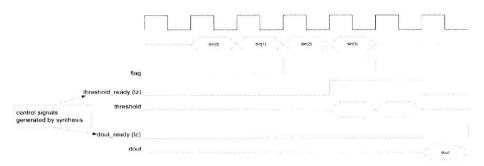

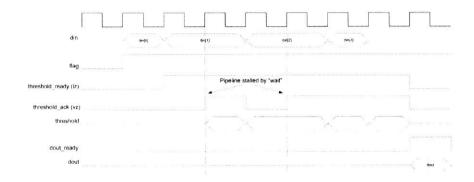

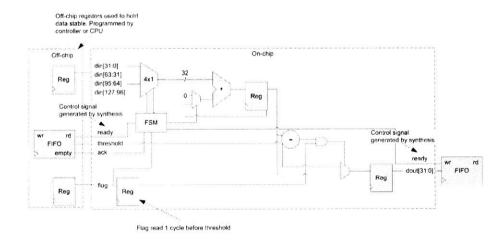

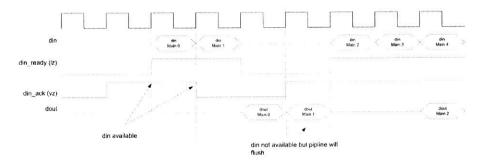

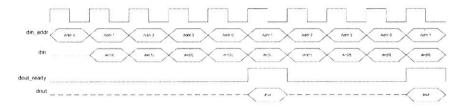

| Ready/acknowledge Behavior (wait)130                        |

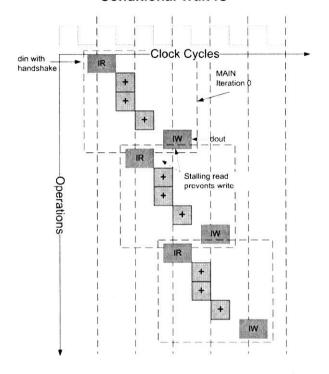

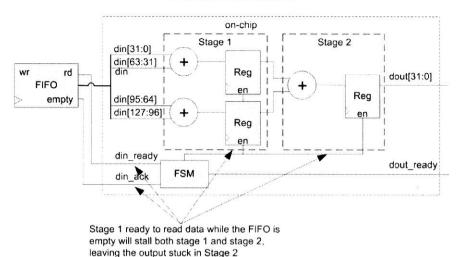

| Stalling the Pipeline131                                    |

| Manually Flushing the Pipeline134                           |

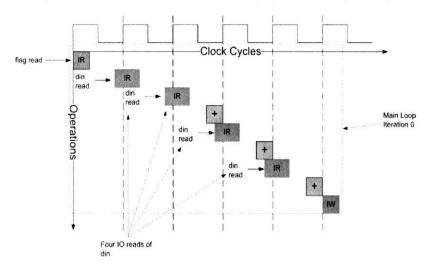

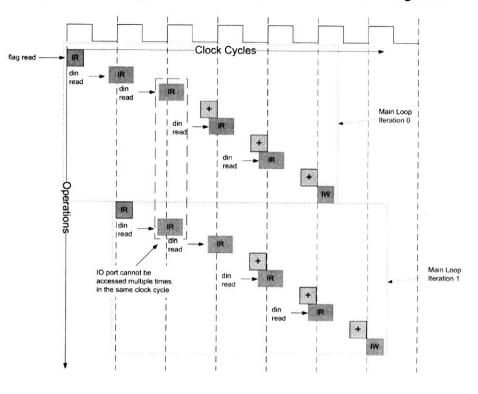

| Writing IO for Throughput135                                |

| Making IO Mergable138                                       |

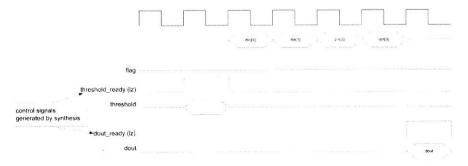

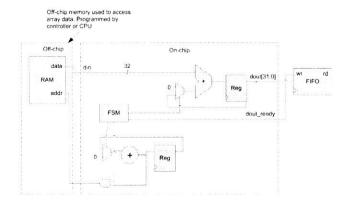

| Memories140                                                 |

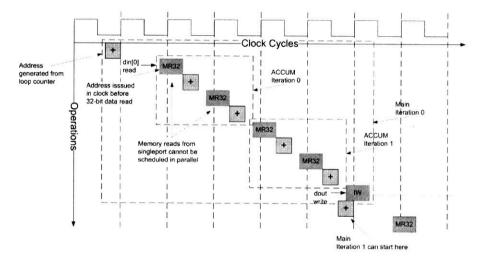

| Automatic Mapping of Arrays to Memories141                  |

| Automatic Memory Merging143                                 |

| Designing for Throughput When Using Memories146             |

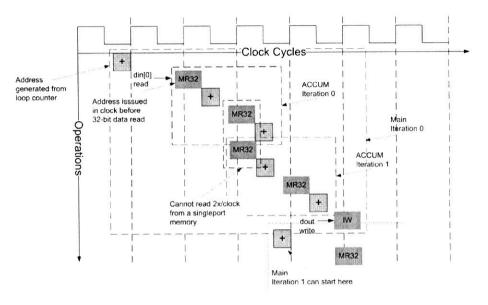

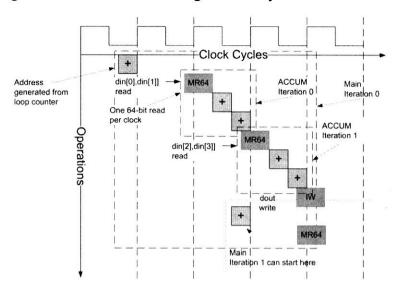

| Non-Mutually Exclusive Memory Accesses146                   |

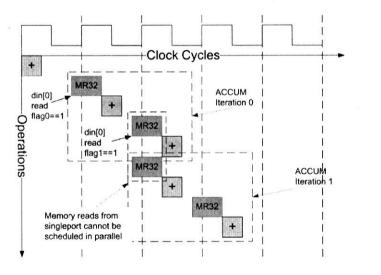

| Making Memory Accesses Mutually Exclusive147                |

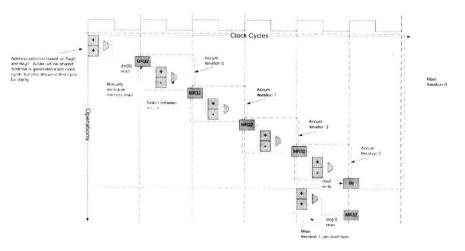

| Manually Merging Non-Mutually Exclusive Memory Accesses 149 |

## Chapter 6 Sequential and Combinational Hardware

| Constant Shifts191                                              | Arrays Shared Between Blocks                              | 239 |

|-----------------------------------------------------------------|-----------------------------------------------------------|-----|

| Transforming Barrel Shifters into Constant Shifts191            | Out-of-order Array Access                                 | 239 |

| Transforming Dynamic Bit Masking192                             | Arrays Mapped to Registers                                | 241 |

| Adder Trees193                                                  | Arrays Mapped to Memories                                 | 243 |

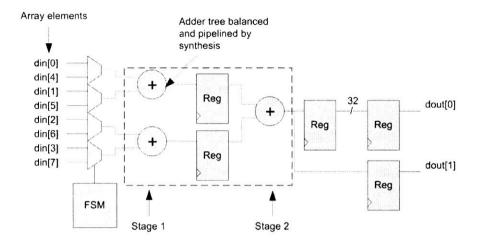

| Automatic Tree Balancing193                                     | In-order Array Access                                     | 245 |

| Preventing Automatic Tree Balancing194                          | Automatic Streaming                                       | 245 |

| Coding to Facilitate Automatic Tree Balancing196                | Algorithmic C Channel Class                               | 247 |

| Lookup Tables (LUT)197                                          | Declaration                                               | 248 |

| References201                                                   | Channel Read: T read()                                    | 249 |

|                                                                 | Channel Write: write(T)                                   | 249 |

| Chapter 7                                                       | Channel data available: available(int N)                  | 250 |

| Memory Architecture                                             | Using Explicit Channels                                   | 250 |

| Introduction203                                                 | Using Channels at the Top-level Interface and Testbench   | 251 |

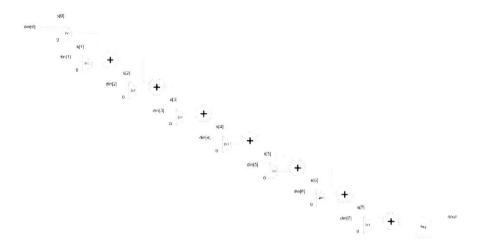

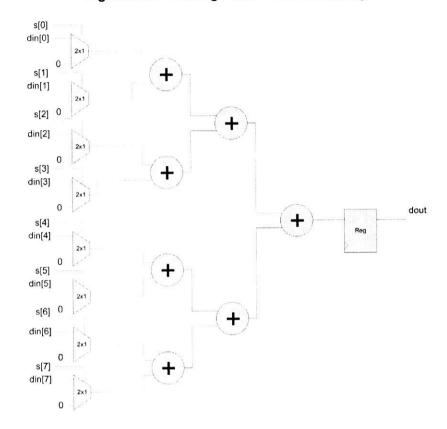

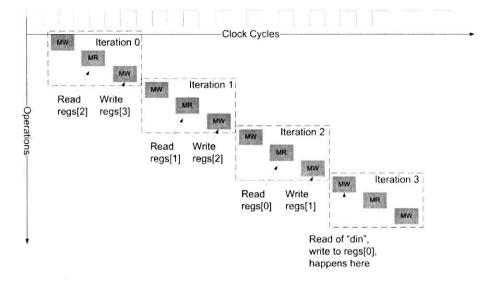

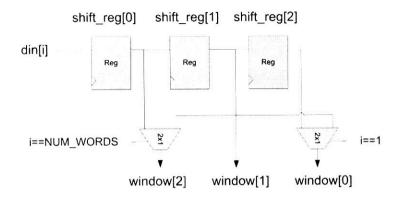

| Memory-based Shift Register203                                  | Blocks with Common Interface Control Variables            | 254 |

| Classic Shift Register Description mapped to Memories204        | Passing Control Variables Between Blocks                  | 254 |

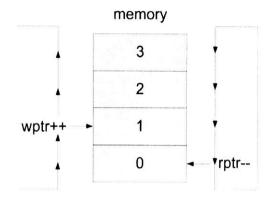

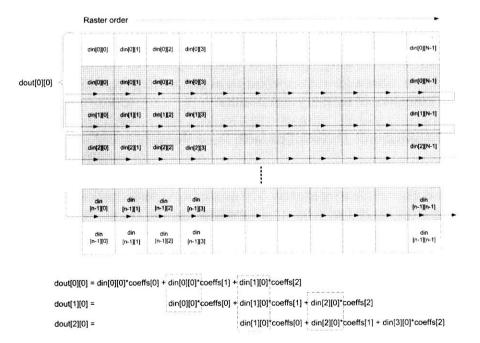

| Circular Buffer205                                              | Connecting Interface Control Variables to Multiple Blocks | 256 |

| Initialization loops207                                         | Duplicating Control IO                                    | 258 |

| Memory Organization208                                          | Reconvergence: Balancing the Latency Between Blocks       | 260 |

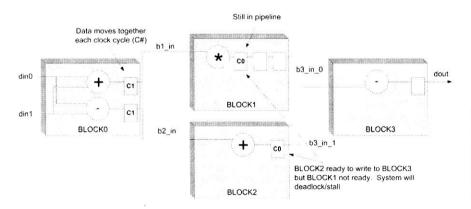

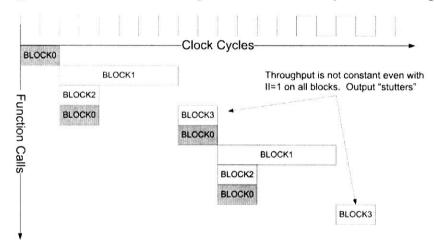

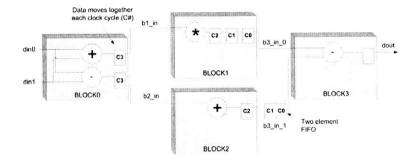

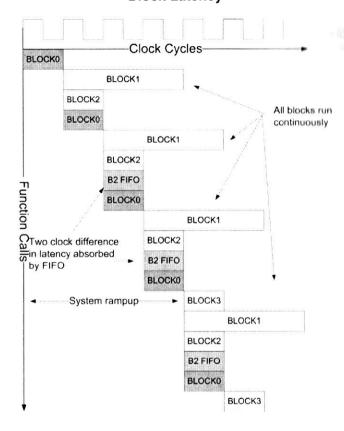

| Interleaving Memories208                                        | Deadlock                                                  | 261 |

| Automatic Interleaving209                                       | Automatic Pipeline Flushing                               | 263 |

| Manual Interleaving with Random Access210                       | Manually Setting FIFO Depths                              | 263 |

| Manual Interleaving with Sequential Access214                   |                                                           |     |

| Widening the Word Width of Memories217                          | Chapter 9                                                 |     |

| Automatic Word Width217                                         | Advanced Hierarchical Design                              | 267 |

| Manually Increasing Word Width with Sequential Access218        | Introduction                                              | 267 |

| Caching223                                                      | ac_channel Methods                                        | 267 |

| Using True Single Port RAM as a Dualport RAM223                 | Channel size: int size()                                  | 267 |

| "Windowing" of 1-D Data Streams227                              | Non-blocking Read: bool nb_read(T &val)                   | 268 |

| Pure Algorithmic Description with Poor Memory Architecture. 227 | Recommended Coding Style                                  | 268 |

| Analyzing Array Access Patterns229                              | Arbitration                                               | 270 |

| Shift Register Sliding Window Implementation230                 | Preventing C++ Assertions from Reading Empty Channels.    | 277 |

| Boundary Conditions231                                          | Feedback                                                  | 277 |

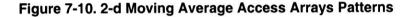

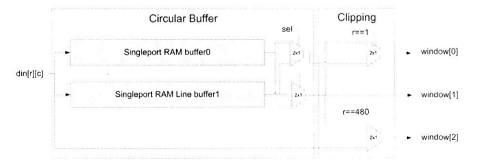

| 2-D Windowing233                                                | C++ Assertion                                             | 278 |

| Pure Algorithmic Description with Poor Memory Architecture.233  | Deadlock                                                  | 280 |

| Circular Line Buffer Sliding Window Implementation235           | Variable Rate or Data Dependent Feedback                  | 281 |

| Chapter 8                                                       | Chapter 10                                                |     |

| Hierarchical Design239                                          | Digital Filters                                           | 283 |

| Introduction239                                                 | Introduction                                              | 283 |

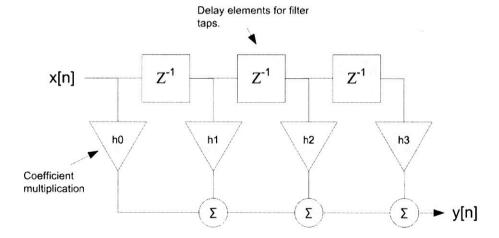

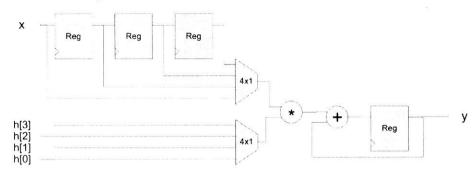

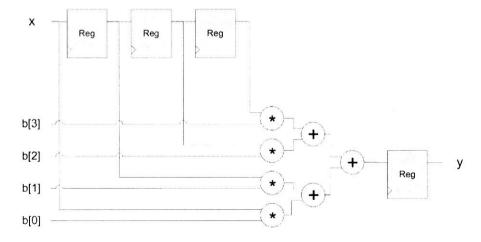

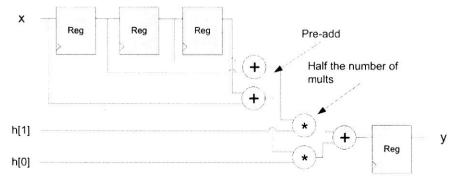

| FIR Filters                              | 283 |

|------------------------------------------|-----|

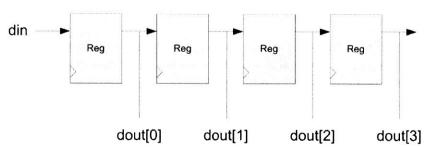

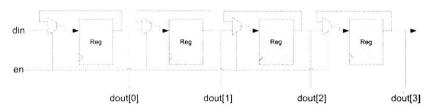

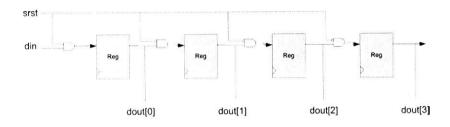

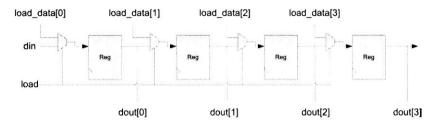

| Register Based Filters                   | 284 |

| External Coefficients                    | 284 |

| Constant Coefficients                    | 286 |

| Loadable Coefficients                    | 287 |

| Symmetric Coefficients                   | 288 |

| Even Symmetric                           | 288 |

| Odd Symmetric                            | 290 |

| Transposed                               | 291 |

| Systolic                                 | 293 |

| Multi-rate Filtering                     | 296 |

| Decimation                               | 296 |

| Algorithmic Decimation                   | 296 |

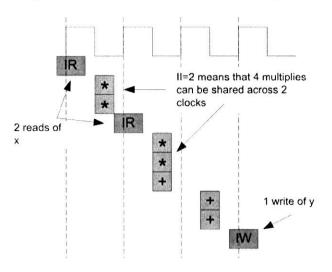

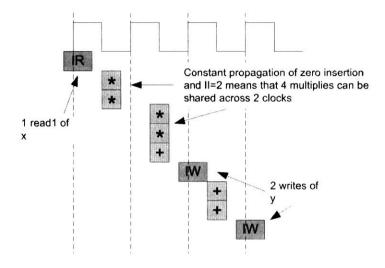

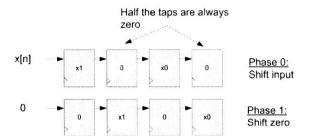

| Manual Decimation                        | 299 |

| Interpolation                            | 304 |

| Algorithmic Interpolation                | 304 |

| Manual Interpolation                     | 306 |

| Multi-stage Decimation                   | 308 |

| Multi-block                              | 309 |

| Single-block                             | 310 |

| Manual Scheduling of Two Stage Decimator | 314 |

|                                          |     |

| Chapter 11                               |     |

| FFT Transform                            |     |

| Introduction                             |     |

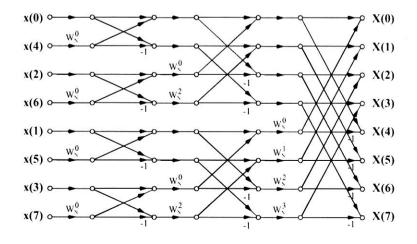

| Radix-2 FFT                              |     |

| Floating Point Radix-2 In-place FFT      |     |

| References                               | 329 |

"You can't always get what you want But if you try sometimes you just might find You get what you need "

The Rolling Stones

### **Preface**

As a former RTL designer who made the switch to High-Level Synthesis (HLS) years ago, I can still remember both the excitement of discovering a totally new design methodology, as well as the frustration of not knowing what to expect from the HLS tool as I attempted to code increasingly complex designs.

My first exposure to the world of HLS began with a demo of a FIR filter written in C++, and synthesized directly to RTL. This was a design I was very familiar with coming from the world of RTL. After having written numerous hand-coded VHDL and Verilog implementations, I was completely blown away when I saw how a single algorithmic C++ description could be used to generate a large number of RTL implementations, each with different area/performance characteristics. The HLS tool was able to do in a matter of minutes, what normally would take me days or weeks to accomplish. The fact that it was then able to take the resulting RTL and simulate it using my C++ testbench to prove functionality was simply unbelievable. The potential of the technology was too attractive for me not to make the switch, and I soon found myself working in the field of HLS.

As I began to tackle more complex designs, I started to encounter occasional problems with achieving the best possible results. What I saw was that the style in which my C++ was written could have a big impact on the resulting quality of the RTL. I would liken this to what I had experienced when people were first making the switch from schematic based design to RTL, where proper coding style was critical to good quality of results. Fortunately for me, I was working with a number of experts in HLS who I could rely on to provide the explanation as to why a particular coding style gave less than desirable results, and who could suggest a better way to write the C++. I was lucky since at that time there was no formal style guide for writing C++ for synthesis.

As HLS has matured the quality of results has improved dramatically for a much wider range of C++ coding styles. However, this does not mean that all styles are equal, and there is still the potential for ending up

with poor quality RTL when the C++ is not well written. Good style not only requires an understanding of the underlying hardware architecture of an algorithm, so that it is reflected in the C++ design, but also an understanding of how HLS works.

This book presents the recommended coding style for C++ synthesis that results in good quality RTL. Most of the C++ examples are accompanied with hardware and timing diagrams, where appropriate. The basic concepts of HLS are introduced and an effort is made to relate them directly to concepts that are well understood by RTL engineers. Although this book focuses primarily on C and C++ to illustrate the fundamentals of C++ synthesis, all concepts presented here are equally applicable to SystemC when describing the core algorithmic part of a design. Although the examples are simplistic in many cases, they illustrate the fundamental principles behind C++ hardware design. These concepts will translate to much larger designs.

As a final thought for the RTL Designers, System Architects, and Algorithm Designers who are looking to adopt High-Level Synthesis; correct-by-construction RTL synthesized from C++ may not look exactly like what you would code by hand. HLS optimizations often can result in the odd logic gate in the resulting schematic. The hardware diagrams in this book exclude all of the extraneous logic. You will probably end up saying at some point that "It's not exactly what I expected the RTL to look like". However you should also ask yourself "How long would it have taken to write using hand-coded RTL?", "Would it have simulated correctly the first time?" and ultimately "Is it good enough?". If you don't get too caught up in the details you'll find the results to be exactly what you need.

Mike Fingeroff, January 2010

#### Who Should Read This Book

Engineering managers should read Chapter One to understand how HLS evolved from existing design methodologies and how it can help improve current design flows. RTL designers should read the entire book and System/Algorithm designers should read chapters 3, 4, 5, 8, and 9, at the very least.

#### **About the Authors**

Mike Fingeroff has worked as a technical marketing engineer for the Catapult C product line at Mentor Graphics since 2002. His areas of interest includes DSP and high-performance video hardware. Prior to working for Mentor Graphics he worked as a hardware design engineer developing real-time broadband video systems. Mike Fingeroff received both his bachelors and masters degrees in electrical engineering from Temple University in 1990 and 1995 respectively.

Thomas Bollaert is product marketing manager for the Catapult C product line at Mentor Graphics. He has a more than 15 years of experience in EDA, and an extensive background in system-level design and high-level synthesis. More recently, Thomas worked in tight collaboration with Mentor Graphics' European customers, helping them learn, adopt and deploy high-level synthesis to improve their design practices. He earned his electronic engineering degree from ESIEE Paris where he specialized in hardware architectures for signal processing applications.

# **Acknowledgements**

I would like to thank all of the people that contributed to the creation of this book by taking their valuable time to review the content and provided essential feedback.

Emmanuel Liegeon, Thales Alenia Space Mathieu Lebon, Alyotech Katsunobu Natori, Hitachi Ltd.

Special thanks to Shawn McCloud, the High-Level Synthesis Product Line Director at Mentor Graphics, for providing me with the time and resources to write this book.

I would also like to thank all of my co-workers at Mentor Graphics for providing internal review of the book: Suravinth Sundralingam, David Burnette, Tony Vandinh, Mike Bradley, Mike Hilsen, and Bob Condon.

Lastly I would like to thank Thomas Bollaert for his contribution of the first chapter of this book as well as his input on the cover artwork. Thanks to Lucien Murray-Pitts for both his review and contribution to the technical content. Special thanks to Bryan Bowyer and Peter Gutberlet for answering numerous questions about HLS and coding style. Thanks to Ron Plyler for his discussion on pipeline feedback, and finally thanks to Andres Takach, Stuart Clubb, and Tom Nagler for their contributions to the chapter on FFT transforms.

# **Chapter 1**

## **Making the Case for High-Level Synthesis**

The promise of high-level synthesis (HLS) is a powerful one: the ability to generate production-quality register transfer level (RTL) implementations from high-level specifications. In other words, HLS automates an otherwise manual process, eliminating the source of many design errors and accelerating a very long and iterative part of the development cycle.

#### A broken design flow

To fully understand the potential and benefits of HLS it is important to put things in the perspective of a hardware design flow. Today, most projects start with some form of specification. Sometimes this is a simple, written document, but quite frequently an executable model is created—usually in ANSI C, C++ or SystemC. At this early stage, the specification is essentially functional: it contains little to no hardware implementation details, and its primary purpose is to validate and fine-tune the desired behavior. Once tested, this behavioral model undergoes a several step process until it takes the form of the actual hardware implementation. The first step is to define an optimal architecture to implement the desired functionality. If the functionality defines "what" the system does, the architecture defines "how" the system does it, with direct consequences on performance, area, and power consumption. After the architecture is defined, the design team hand-codes these decisions in the form of a Verilog or VHDL RTL description.

This is where the biggest problem lies. Finding a suitable architecture is not a simple task, and finding an optimal one is even more challenging. But the fundamental issue is the manual nature of this entire approach. As clever as we can be and no matter what we do, our curse, as engineers, is to trip over these tiny yet enormously frustrating things we've dubbed "bugs." Simply put, any manual intervention is a source of errors. Suddenly, what was initially a straightforward process from specification to implementation becomes a nightmarish iterative cycle. The hand-coded RTL design is tested, bugs are reported, and time is spent trying to hunt

them down and fix them individually—only to move on to the next bug. This could be an endless process if it didn't have to end at some point to meet deadlines.

#### Keeping up with the pace

The issue of course is exacerbated by growing design sizes. The bigger the system and the more complex the application, the more chances of errors and the harder it becomes to stay on schedule. Unfortunately, ever-increasing complexity is one of the few certainties in electronic design.

Just remember the kind of equipment we had fifteen years ago, whether cell phones or televisions. Now compare them with today's commensurable items. Their evolution has been so dramatic that we don't even call them the same thing anymore! We now have "smart phones" in our pockets and "high-definition home entertainment systems" in our living rooms. Everything has changed to become more sophisticated, more complex. Likewise in the electrical engineering: technology nodes and process geometries keep shrinking, clock frequencies keep increasing, embedded cores keep multiplying, and verification methodologies are borrowing object-oriented concepts from the software community. Everything has changed.

Everything but one thing: the RTL creation process. We are trying to develop 4G broadband modems with tools and methods inherited from the mid-90s, when GSM was the hot topic. We are trying to create H264 decoders with languages adopted to design VGA controllers. Something is deeply broken. We simply can't create RTL efficiently enough; eventually, bugs trigger and problems fire during the verification phase. It is no surprise if verification is now the bottleneck in any ASIC project.

#### Benefits of high-level synthesis

High-level synthesis addresses the root cause of this problem by providing an error-free path from abstract specifications to RTL. By using HLS, design teams greatly accelerate design time while also reducing the overall verification effort.

#### Reducing design and verification efforts

When working at a high-level of abstraction a lot less detail is needed for the description. For instance, at the functional level, engineers do not need to worry about implementation details such as hierarchy, processes, clocks, or technology. They are free to focus only on the desired behavior. This makes the description much easier to write. With fewer lines of code, the risk of errors is greatly reduced, and with fewer things to test for in the source, it is easier to exhaustively verify the model.

After the high-level model is written and verified, HLS automates the RTL implementation process. But if HLS tools eliminate manual interventions and errors, they do not eliminate engineering intervention. That is, decisions still need to be made. With high-level synthesis, engineers remain in control; they make the decisions and the HLS tool implements them. They simply have a more efficient and productive way of getting their job done. For instance, the designer decides upon the proper level of parallelism for an optimal architecture and constrains the HLS tool accordingly. In turn, the tool takes care of allocating and scheduling the needed hardware resources, building the datapath and control structures to produce a fully functional and optimized implementation. With HLS, correct RTL is obtained more rapidly, shortening the creation phase. In turn, the debug overhead is lowered and the verification burden is reduced.

#### More effective reuse

Working at a higher level of abstraction has an additional benefit. The design sources are now truly generic and therefore more versatile. For years, IP and reuse have been promoted as ways to address the design complexity challenge. But these strategies find their limits. RTL views describe what happens between two clocks edges. By definition this is tied to a specific technology and clock frequency. If retargeting legacy RTL is often possible, it is usually done at the expense of power, performance and area. Moreover making small changes to an existing IP to create a derivative can quickly turn into a much bigger project than anticipated. In contrast, when working with purely functional specifications, there are no such details as clocks, technology or micro-architecture in the source. This is information added automatically during the high-level synthesis

process. And if new functionality is added to the IP, changes can be made and verified more easily in the abstract source and without the fear of breaking a pipeline or having to rewrite a state machine. With HLS it is much simpler to reuse and retarget functional IP.

#### Investing R&D resources where it really matters

There are many other advantages to using high-level synthesis, but what is especially interesting is to look at the induced benefits. When properly used, HLS flows can help save months of R&D effort. With engineering resources spending fewer cycles on RTL coding and verification, more time can be spent on differentiating activities. RTL coding is a necessity, not a value-added activity. In comparison, algorithm development, architecture optimization, and system-level power optimization can really make a difference in the success of a product. Time-to-market often matters, but it is just one part of the equation. Feature superiority, cost competitiveness, and power consumption are also critical success factors. By using HLS, organizations can spend less effort dealing with mundane design tasks and invest more intelligence where it matters most.

#### Seizing the opportunity

High-level synthesis is not a new idea. The promise of designing in a better way is as old as EDA itself. The evolution towards higher abstractions is rooted in EDA's DNA. The industry constantly strives to raise the abstraction level, easing the design process for engineers around the world. When moving from transistor to gates, and then from gates to RTL, we did nothing other than adopt more efficient and higher-level hardware design methods. Today, once more, the design pressure is too high to resist the call for change.

Since the early commercial and academic work, HLS has come of age. A new generation of C synthesis tools reached the market in 2004. Since then, countless user testimonials and hundreds of tape-outs have confirmed not only the viability but also the necessity of HLS for modern ASIC design. Over the past few years, HLS tools have developed and added the necessary technology to become truly production-worthy. Initially limited to datapath designs, HLS tools have now matured to

address complete systems, including control-logic, and complex SoC interconnects—without a penalty in quality of results.

The value of HLS has clearly been established and the technology routinely delivers on the expectations. High-level synthesis provides great benefits, but is also a disruptive technology. It implies change in the methodologies, in the design processes, and to some extent, in the skills required. The learning curve is the last barrier to wider adoption. The move to HDL languages didn't happen overnight either. Designers learned from books, references materials, and real-world examples, earning their RTL know-how over many years. The same is happening now for high-level synthesis. Early adopters have anchored HLS in their design flows and are paving the way for mainstream users.

This book will help designers travel this HLS road. It is meant to be a practical and valuable companion for engineers seeking to adopt high-level synthesis. The HLS promise awaits, the technology delivers it, and this book helps you seize and implement this necessary and more productive path to verified RTL.

Thomas Bollaert, January 2010

# Chapter 2

## General C++ Style

#### Introduction

The purpose of this C++ synthesis style guide is to provide a firm foundation for writing good quality synthesizable C++ code. This includes not only recommendations for achieving good quality of results in hardware, but also good programming practices to ensure "clean" code that passes compilation, execution, and RTL/C++ co-verification.

#### File Organization

This style guide covers general coding guidelines, including how to organize and structure the files that make up a design. This is only intended as an example recommendation and users are free to choose and use any structure that is comfortable, or required by their institution. The main intent here is to guide the user to adopting and adhering to a methodology that makes managing their designs easier.

An example directory structure for organizing your C++ files along with Catapult project files should look something like:

#### Where:

- "Project directory" is the current design directory

- "src" directory contains all C++ (\*.cpp, \*.cxx, \*.C, \*.h, \*.hpp) source and header files and the Makefile. This is where the executable is compiled and linked

- "ccs" contains the synthesis \*.tcl scripts

- "dat" directory contains any file I/O for the testbench

- · "sim" directory is for Matlab and Simulink projects and scripts

#### **Building an Executable Using Makefiles**

Make is a Unix utility that is used to automate the compilation of a set of files into an executable. Although it is not necessary to use Makefiles, it is highly recommended, and streamlines the compilation and linking process. Make has default rules it knows about and enforces, such as understanding file dependencies and guaranteeing that files are recompiled when a dependency changes. (For a more complete guide to creating makefiles see http://www.gnu.org/software/make/manual)

#### **Makefile Naming**

The "make" utility looks for a file called "Makefile" by default. If this file is not found it then looks for a file called "makefile". You can also specify an arbitrary filename by using the "-f" command line switch for Make.

#### Comments

Comments are denoted by preceding text with the pound (#) sign. Any text following the "#" sign untill the end of the line is treated as a comment.

```

# Example Makefile

```

#### Macros

Macros can be defined in a Makefile that allow substitution of complex expressions. For example:

```

CXX = /usr/bin/g++

```

#### **Targets**

The basic makefile is composed of a set of rules.

```

targets : prerequisites command

```

The targets are file names and must be separated by spaces. The command lines must start with a tab character, and the prerequisites, also known as dependencies, consist of file names separated by spaces. The dependencies are used to test when a target is out of date.

#### **Phony Targets**

A phony target is simply a way to enforce commands to be executed regardless of whether a file of the same name exists in the Makefile directory. Thus the target will always execute even if a file of the same name is up to date.

```

.PHONY: clean clean: rm *.o *.exe

```

#### Simple Makefile Example

Consider the simple example where the design consists of three files:

- hello.cpp src directory file with a function that prints hello

- hello.h include directory file that contains the function prototype

- main.cpp testbench that calls the hello.cpp function.

A very basic Makefile to compile these files into an executable is shown in Example 2-1.

#### Example 2-1. Simple Makefile

```

#phony target to remove all objects and executables

.PHONY: clean

clean:

rm -f *.o *.exe

```

An improvement of the very simple Makefile shown in Example 2-1would be to take advantage of the use of macros and also the implicit dependency in Make between \*.o files and \*.cpp or \*.cxx files. This is shown in Example 2-2.

#### **Example 2-2. Makefile Using Macros**

```

# Example Makefile

#MACROS

CAT HOME = $ (MGC HOME)

TARGET

= my tb

OBJECTS

= main.o hello.o

DEPENDS

= hello.h

INCLUDES = -I''$ (CAT HOME)/shared/include"

DEFINES

= /usr/bin/q++

CXXFLAGS = -g - o3 \$ (DEFINES) \$ (INCLUDES)

$(TARGET): $(OBJECTS)

$(CXX) $(CXXFLAGS) -o $(TARGET) $(OBJECTS)

$(OBJECTS): $(DEPENDS)

#phony target to remove all objects and executables

.PHONY: clean

clean:

rm -f *.o *.exe

```

#### Header/Include Files

In C++ programming a header file typically contains forward declarations of classes, function prototypes, and other information shared by multiple source files. Although variables can be declared within a header file, making them global, this is not recommended. One of the most common high-level synthesis uses for header files is for creating type and constant definitions. Example 2-3 shows the header file for the hello.cpp example discussed in the previous section.

#### Example 2-3. Header File

```

1 //guard string to prevent multiple inclusion 2 #ifndef \_ HELLO \_ #define \_ HELLO

```

```

4

5  //Forward declaration of function

6  void hello();

7

8  const int ITERATIONS = 22;

9

10  typedef int dType;

11

12  #endif

```

The details of Example 2-3 are:

- Lines 2 and 3 implement a guard string that prevents multiple inclusion of the header file. The first time the header file is compiled "\_\_HELLO\_\_" will be defined, preventing further inclusion.

- Line 6 defines the function prototype for the "hello" function implemented in hello.cpp. Including this header file within another design makes the "hello" function available.

- Line 8 defines a constant integer "ITERATIONS" and sets it equal to 22. This could also have been done using a #define but it is not recommened. Use of #define should only be used when absolutely necessary. Defining constants using #define can lead to cryptic errors during compilation if the user is not careful.

- Line 10 uses a type definition to define a new type "dType" to be type int. This is very useful in that it allows the design data types to be decoupled from the implementation code. This mechanism can be used to easily switch between data types.

Example 2-4 shows the hello.cpp design which includes the header file.

#### Example 2-4. Including the Header File

```

#include <iostream>

using namespace std;

//Including user defined header file

#include "hello.h"

void hello() {

//dType defined in header file

dType tmp;

//ITERATIONS defined in header file

for(int i=0;i<ITERATIONS;i++) {

tmp = i;

cout << "Hello" << tmp << endl;

}

</pre>

```

The details of Example 2-4 are:

- Line 4 includes the design header file

- Line 10 uses the constant "ITERATION" defined in the header file.

Example 2-5 shows the design testbench for the hello.cpp design. This file also includes the header file which gives it access to the function prototype which is instantiated on line 4.

#### Example 2-5. Testbench

```

//Include user header file

#include "hello.h"

3

int main(){

hello();

```

#### **Test Benches**

The user testbench is a C++ design that is used to test the device under test (DUT) for functional correctness. In a HLS design environment the C++ testbench is typically used to test both the C++ and the RTL, so it is important to follow good programming practices. Furthermore it is critical to leverage the C++ testbench to prove that the DUT matches the original algorithm as code changes are made. There is nothing worse than re-writing your C++ code to get good synthesis results only to find out that you have broken the functionality. Be smart, be methodical, and verify your design at every step.

#### If you don't have a C++ testbench, write one. Otherwise you're wasting valuable time.

#### Creating a Golden Reference Design

One of the first things a new HLS user discovers is that they have to make code changes to their original floating or fixed point source code. These code changes are made to improve quality of results (QofR) and/ or pass synthesis. The biggest mistake that users can make is to take their algorithmic C++ code and start modifying it for synthesis without having created a backup reference to compare the changes against. It only takes a few code changes to completely break a design.

Consider the following design shown in Example 2-6:

#### Example 2-6. C++ with Conditional Branches

```

#include "test.h"

void test(dType a[2], dType b[2], dType dout[2], bool sel){

if(sel){

dout[0] = a[0] + b[0];

dout[1] = a[1] + b[1];

dout[0] = a[0] - b[0];

dout[1] = a[1] - b[1];

```

Examination and/or synthesis of the "test" function shown in Example 2-6 reveals that the IO accesses on a, b, and dout creates a performance bottleneck if the interfaces are memory interfaces (The reasons for this performance bottleneck is discussed in later chapters). Rewriting the code allows for better performance, but rather than modifying the original code, a new design is created which allows a comparison to the original algorithm.

# Note -

Always make a copy of the original algorithm to verify against any code changes when possible. It may not be possible to do a bit-for-bit comparison for some algorithms.

The re-written design, which is functionally equivalent to the original, is shown in Example 2-7.

#### Example 2-7. Modified Design

```

#include "test mod.h"

void test mod(dType a[2], dType b[2], dType dout[2], bool sel){

for (int i=0; i<2; i++) {

if(sel){

dout[i] = a[i] + b[i];

}else{

dout[i] = a[i] - b[i];

```

The testbench should be modified to check the modified design against the original algorithm, shown in Example 2-8.

#### **Example 2-8. Modified Testbench**

```

#include <iostream>

using namespace std;

#include "test.h"

#include "test mod.h"

int main(){

dType a[2] = \{10, 20\};

dType b[2] = \{10, 20\};

dType dout [2];

dType dout mod[2];

10

bool sel = true;

bool error = false;

//DUT original

13

test(a,b,dout,sel);

14

//DUT modified

15

test mod(a,b,dout mod,sel);

16

17

for(int i=0; i<2; i++){

if(dout mod[i] != dout[i]){

19

cout << "ERROR" << endl;

20

error = true;

21

else

23

cout << dout[i] << endl;</pre>

24

25

if(error)

return -1; //indicates test failure

26

27

28

return 0; //test passed

29

```

The details of the modified testbench shown in Example 2-8 are:

- Lines 13 and 15 instantiate the original and modified functions and apply the same set of inputs. Each function produces its own outputs "dout" and "dout\_mod".

- Lines 17 through 24 check each of the outputs from the original design against the modified design to see if they match. If there is a mismatch it's flagged as an error.

- Lines 25 through 28 check to see if any errors occurred and return the test status.

#### Note -

Each time a code change is made the testbench should be rerun to check the change against the original design. Failure to do this may mean hours of debugging to figure out which change broke the design.

#### Make Sure You're Fully Testing the DUT

One of the most common, and costly, mistakes users make when testing the DUT is failing to test all possible conditional branches based on the control inputs into the DUT. This can often lead to discovering functional differences between the DUT and the golden reference after having made significant changes required for synthesis. This is illustrated by looking at the testbench and DUT shown in Example 2-8. The testbench only ever tests the DUT with "sel = 1". "sel" is responsible for selecting one of two possible conditional branches in the DUT. One of the primary reasons for making code changes is when the design cannot be synthesized, or when timing, performance, or area must be improved. If any of these reasons require the code to be rewritten, it is likely that it will force the user to modify all branches of any conditions in the design. The user would be unaware if a functional mistake was introduced in the branch for "sel = 0" after rewriting the code. The testbench should be rewritten as:

#### **Example 2-9. Improved Testbench**

```

#include <iostream>

using namespace std;

#include "test.h"

#include "test mod.h"

int main() {

dType a[2] = \{10, 20\};

dType b[2] = \{10, 20\};

dType dout [2];

dType dout mod[2];

bool sel = true;

for (int j=0; j<2; j++) {

sel = i;

//DUT original

test(a,b,dout,sel);

//DUT modified

test mod(a,b,dout mod,sel);

for(int i=0;i<2;i++){

if(dout mod[i] != dout[i])

cout << "ERROR" << endl;

else

cout << dout[i] << endl;</pre>

```

Now the DUT is tested for both values of "sel" covering both conditional branches.

#### **Uninitialized Variables**

In general a variable should never be read before it is written. Uninitialized variables are treated differently by different compilers and synthesis tools, often leading to unpredictable results. Many hours can be wasted trying to track down simulation bugs only to discover that the source of the problem is an uninitialized variable. Another common side effect is to have entire sections of a design optimized away because variables are not initialized. Consider the following design:

#### **Example 2-10. Uninitialized Variables**

```

void acc(int din[4], int &dout){

int tmp;

for(int i=0;i<4;i++)

tmp += din[i];

dout = tmp;

}</pre>

```

Line 2 of Example 2-10 defines a variable "tmp" that is left uninitialized. Line 4 then uses "tmp" to accumulate the array "din". Since "tmp" is not initialized it can be considered as a "don't care", which means that the first accumulate looks like "tmp = (don't care) + din[i]". This can lead to a unexpected result. Most compilers will flag this as a warning if verbose messaging is enabled. E.g. "g++ -v...".

#### Note -

# Chapter 3 Bit Accurate Data Types

#### Introduction

Algorithm designers, system architects, and RTL engineers have been using bit-accurate data types for years to model true hardware behavior. The need for bit-accuracy becomes especially obvious now that designers are building hardware directly from C++, whose native types only come in widths of 1, 8, 16, 32, etc, bits. Many existing bit accurate data types used today are "home grown" class libraries that evolved within companies, and model bit accuracy using traditional shift and mask techniques. Although these "home grown" types may be faster for simulation, they are typically very slow for synthesis, and can also give much poorer quality of results than the industry standard bit-accurate data types.

To date there are two industry standard bit accurate data types; the SystemCTM and Mentor Graphics Algorithmic C data types. Although SystemC was developed first, the implementation of its bit-accurate data types suffers from a number of issues, the biggest being long execution runtimes. Because of this, customer demand drove Mentor to develop their own bit-accurate types, which have now become the most widely used data types in high-level synthesis. The Algorithmic C data types not only simulate much faster than the SystemC types, but give better quality of results for synthesis over "home grown" bit accurate types. Algorithmic C data types are also consistent between C++ and RTL simulation. So whatever you build in C++ matches the true hardware behavior. In light of this, the focus of this chapter is on the use of the Algorithmic C data types. Furthermore, this chapter only attempts to provide enough of an overview of the Algorithmic C data types to begin designing in C++. A comprehensive manual is available at:

http://www.mentor.com/products/esl/high\_level\_synthesis/ac\_datatypes

#### Compilation, Debug, and Simulation Speed

In order to compile and use the Algorithmic C data types the header file for either the integer data types, ac\_int, or fixed point data types, ac\_fixed, must be included in the C++ source file(s).

```

#include <ac_int.h>

#include <ac fixed.h>

```

It is also critical to achieving the fastest runtimes that the highest level of optimization is set (-O3 in gcc and /Ox in MS Visual).

```

g++ -O3 -I <path to Algorithmic C data types> -o hello.exe hello. cpp \,

```

When debugging bit accurate code using gdb, ddd, or any of the MS Visual tools it is best to disable optimizations and turn on verbose warnings. E.g.

```

g++ -g -Wall -I <path to Algorithmic C data types> -o hello.exe hello.cpp \,

```

#### **Header Files and Typedefs**

Although the Algorithmic C data types execute much faster than the SystemC data types, they will in general run slower than the native C++ types. For this reason, as well as simplifying debugging, it is often desirable to be able to quickly switch between Algorithmic C and native C++ data types. The easiest way to do this is to define all variables in a global header file for both Algorithmic C and native types and use compiler defines to switch between the two definitions. Example 3-1 shows a header file that uses a compiler define "NATIVE\_TYPES" to select between the type definitions of "dType" and "oType" as either native C++ types or Algorithmic C data types. This header file is then included in Example 3-2, which defines all its variables in terms of the type defined variables.

#### **Example 3-1. Header File with Typedefs**

```

1 #ifndef __TYPEDEFS_

2 #define __TYPEDEFS_

3 #include <ac_int.h>

```

```

#ifdef NATIVE_TYPES

typedef short int dType;

typedef int oType;

#else

typedef ac_int<7,true> dType;

typedef ac_int<14,true> oType;

#endif

#endif

```

#### **Example 3-2. Using Type Defined Variables in a Design**

```

14 #include "typedefs.h"

15 void test(dType a, dType b, oType &c){

16    oType tmp;

17

18    tmp = a*b;

19    c = tmp;

20 }

```

#### **Integer Data Types**

The Algorithmic C integer data types allow designers to model a signed or unsigned bit vector with static bit precision. This closely matches what RTL designers can do today with VHDL and Verilog 2001. The ac\_int data types are templatized, and allow designers to specify both the width and signedness of variables.

#### **Unsigned integer**

The Algorithmic C unsigned integer data types are declared as:

```

ac_int<W,false> x;

where:

W = Bit width

0 <= x <= 2W-1 by increments of 1</pre>

```

Any value assigned to "x" that is either greater than the maximum representable value, or negative in this case, will overflow or "wrap" around. This is the same behavior that RTL designers are familiar with today when creating counters. Example 3-3, which is purely for simulation, shows the use of a 7-bit unsigned integer to create a sign wave.

#### **Example 3-3. Algorithmic C Unsigned Integer**

```

#include <ac int.h>

#include <fstream>

#include <cmath>

using namespace std;

const double pi = 3.14;

const int OFFSET = 64;

int main(){

fstream fptr;

fptr.open("tmp.txt", fstream::out);

ac int<7, false> x[128];

11

for (int i=0; i<128; i++) {

x[i] = OFFSET + 63*sin(2*pi*i/64);

13

fptr << x[i] <<endl;</pre>

14

15

fptr.close();

16

17

```

The details of Example 3-3 are:

- Line 1 includes the ac\_int library.

- Line 10 declares an array of 7-bit unsigned integers.

- Line 12 computes two cycles of a sine wave and assigns the results to "x[i]". The sine wave amplitude is +/- 63 and it is given a positive offset of 64 to utilize the full dynamic range of "x". This is because a 7-bit unsigned integer can range from 0 to 2^7-1 or 0 to 127. Since the sine function only produces values between 1 and -1 it is necessary to scale it and add the offset before assigning to "x"

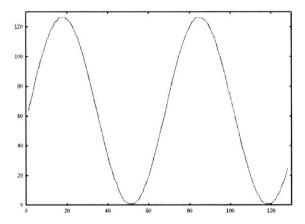

The plot of the sine wave generated in Example 3-3 is shown in Figure 3-1.

Figure 3-1. Maximum Range of 7-bit Unsigned Integer

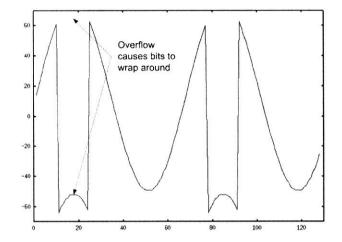

The effects of wrapping in a bit-accurate data type can be seen by replotting the results of Example 3-3 when the offset is increased to 80, shown in Figure 3-3.

Figure 3-2. Effect of Wrapping in Bit-accurate Unsigned Data Types

#### Signed Integer

The Algorithmic C signed integer data types are declared as:

```

ac int<W,true> x;

```

#### where:

$-2W-1 \le x \le 2W-1-1$  by increments of 1

The signed integer bit-accurate data types have similar wrapping behavior as the unsigned integers with the difference being that the signed data types wrap based on the expression shown above. Example 3-4 shows the sine wave generation example where the type for "x" has been changed to signed integer on Line 10. The offset has been set to zero since the negative values are now supported by the data type.

**Example 3-4. Algorithmic C Signed Integer**

```

#include <ac int.h>

#include <iostream.h>

#include <fstream.h>

#include <math.h>

const double pi = 3.14;

const int OFFSET = 0;

int main()

fstream fptr;

fptr.open("tmp.txt", fstream::out);

10

ac int<7, true> x[128];

11

12

for (int i=0; i<128; i++) {

13

x[i] = OFFSET + 63*sin(2*pi*i/64);

14

fptr << x[i] <<endl;</pre>

15

16

fptr.close();

17 }

```

Figure 3-3 and Figure 3-4 show the plots for Example 3-4 with offsets of zero and 14 respectively.

Figure 3-3. Maximum Range of a 7-bit Signed Integer

Figure 3-4. Effects of Wrapping in Bit-accurate Signed Data Types

#### Note -

The plots of both the unsigned and signed data types illustrate the similarity in behavior to designing in RTL. Designers MUST be aware of the dynamic range of the algorithm to avoid "wrapping" of bits. Once this occurs the algorithm results are meaningless.

#### **Fixed Point Data Types**

The Algorithmic C fixed point data types allow designers to model a signed or unsigned bit vector with static fixed point precision. This is something that cannot be done directly in RTL, and is one of the many advantages of high-level synthesis. Although most DSP algorithms are designed using floating or fixed point arithmetic, the actual RTL implementation is done using integers, and the designer has to manually track the decimal point by shifting intermediate results left or right. This is not only a tedious way of designing, but it is also error prone. HLS allows designers to build hardware directly from a fixed point model. The ac\_fixed data types are templatized, and allow designers to specify both the integer and fractional width and signedness of variables.

#### **Unsigned Fixed Point**

The Algorithmic C unsigned fixed point data types are declared as:

```

ac_fixed<W,I,false> x;

where:

0 <= x <= (1-2-W)2I by increments of 2I-W</pre>

```

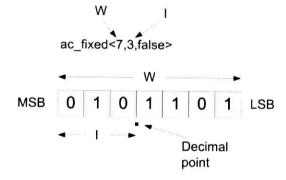

For the fixed point data types both the total width "W" and the number of integer bits "I" are specified. As a result of this "I" determines the location of the decimal point relative to the MSB (Figure 3-5).

Figure 3-5. Fixed Point Decimal Point Position

Now that the Algorithmic C data types have provided the ability to express fractional values, it is no longer necessary to scale results into the integer domain. Taking Example 3-3, which scaled the sine wave up to maximize the dynamic range of 7-bit unsigned integer "x", and expressing it using unsigned fixed point data types leads to Example 3-5.

#### Example 3-5. Algorithmic C Unsigned Fixed Point Data Type

```

#include <ac_fixed.h>

#include <iostream.h>

#include <fstream.h>

#include <math.h>

const double pi = 3.14;

const double OFFSET = 1.0;

int main(){

fstream fptr;

fptr.open("tmp.txt", fstream::out);

ac_fixed<7,1,false> x[128];

```

```

11

12    for(int i=0;i<128;i++) {

13         x[i] = OFFSET + 0.98*sin(2*pi*i/64);

14         fptr << x[i] <<endl;

15    }

16    fptr.close();

17 }</pre>

```

The details of Example 3-5 are:

- Line 1 includes the ac\_fixed data types.

- Line 10 defines a 7-bit fixed point array "x" with one integer bit. This means that values of "x" can range somewhere between 0 and (1-2-7)\*21 or 1.98. Supporting the full amplitude of the sine wave from -1 to 1 would require 2 integer bits.

- Line 13 computes the sine wave and adds an offset of one, keeping all values positive and preventing wrapping by keeping the amplitude of the sign wave from exceeding +/- 0.98.

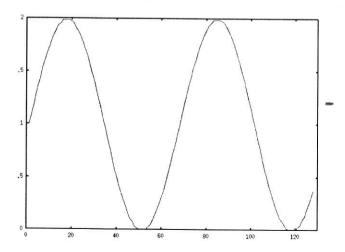

Figure 3-6 shows the plot of the sine wave from Example 3-5.

Figure 3-6. 7-bit Unsigned Fixed Point Sine Wave

#### Signed Fixed Point

The Algorithmic C signed fixed point data types are declared as:

```

ac_fixed<W,I,true> x;

```

where:

```

-0.5*2I \le x \le (0.5-2-W)2I by increments of 2I-W

```

"I" determines the location of the decimal point relative to the MSB, which is also the sign bit.

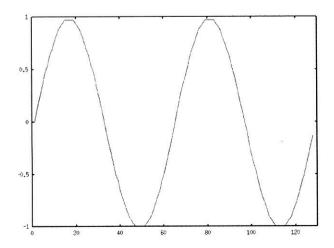

Example 3-6 shows Example 3-5 rewritten to use signed fixed point data types. The offset, which is no longer needed is set to zero. Figure 3-7 shows the plot of the sine wave from Example 3-6, which ranges from almost -1 to 1.

#### **Example 3-6. Algorithmic C Signed Fixed Point Data Type**

```

#include <ac fixed.h>

#include <iostream.h>

#include <fstream.h>

#include <math.h>

const double pi = 3.14;

const double OFFSET = 0.0;

int main() {

fstream fptr;

fptr.open("tmp.txt", fstream::out);

10

ac fixed<7,1,true> x[128];

11

12

for (int i=0; i<128; i++) {

x[i] = OFFSET + 0.98*sin(2*pi*i/64);

13

fptr << x[i] <<endl;</pre>

14

15

16

fptr.close();

17 }

```

Figure 3-7. 7-bit Signed Fixed Point Sine Wave

#### Quantization and Overflow

In addition to allowing algorithms to be expressed more naturally, the fixed point data types also provide mechanisms to deal with quantization and overflow. The default mode for ac\_fixed is to truncate and wrap/overflow, similar to what was shown for ac\_int. The default mode does not cost any additional area but may not be ideal for some applications. There are many quantization and overflow modes supported by the ac\_fixed data types, and they are covered in detail in the Algorithmic C data types manual. This chapter presents the reasons why one might wish to enable these modes. The quantization and overflow modes are enabled using additional template parameters for the ac\_fixed data types.

```

ac fixed<W, I, S, Q, O> x;

```

Where Q and O set the quantization and overflow modes respectively.

#### **Truncation and Rounding**

The default behavior is truncate and to throw bits to the right of the LSB away. This results in a complete loss of information. An example of this would be assigning fractional data to a fixed point variable with only integer bits. E.g.

```

ac fixed<7,7,true> x = 0.5;

```

Printing out the value of "x" after the assignment gives a value of zero, since "x" has no fractional bits. Instead of throwing away the fractional data, a rounding mode can be used to round up or down depending on the fractional value. Similar to what we were all taught in grade school, we can round up or down depending on where the fractional value lands between two integer values.

```

ac fixed<7,7,true,AC RND> x = 0.5;

```

AC\_RND rounds up towards positive infinity, which means that "x" will be assigned a value of one. The rounding mode rounds based on the smallest allowable increment defined by W and I.

#### Saturation and Overflow

The previous examples showed that the default behavior is to have bits "wrap" around when the maximum or minimum representable value is exceeded. This is known as overflow or underflow and is usually a very undesirable situation. Most algorithms can, and should, be designed so that overflow never occurs. This means taking into account the dynamic range of variables and ensuring that the internal bit growth is sufficient to represent all possible ranges of algorithm inputs. However there are situations where it is necessary to ensure that overflow can never occur. Mission critical systems such as flight control would be a good example where overflow would be disastrous. Video algorithms are another example of why overflow would be undesirable, with most people not wanting pixels flipping from the brightest to the darkest colors.

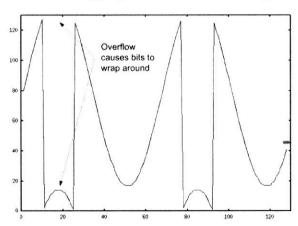

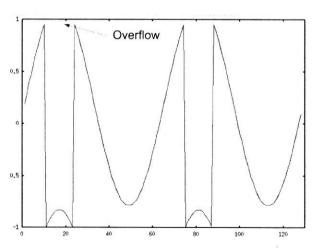

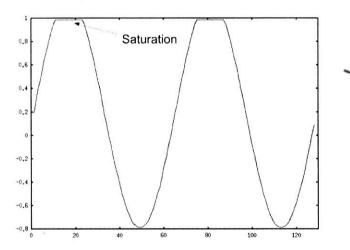

Taking Example 3-6 on page 23 and adding a slight positive offset will cause the result to overflow, leading to a meaningless, or potentially catastrophic, result, shown in Figure 3-8.

Figure 3-8. Fixed Point Overflow

Overflow can be prevented by enabling saturation on the fixed point data type. More details on the behavior of these modes can be found in the Algorithmic C data types manual. Care should always be taken when using saturation since it often increases the area of a design. DO NOT simply turn on saturation on all variables in a design. Saturation

is typically used selectively in a few places. Example 3-6 is rewritten to enable saturation using the overflow template parameter AC\_SAT, shown on line 10 of Example 3-7.

#### Example 3-7. Turning on Saturation in ac\_fixed Data Types

```

#include <ac fixed.h>

#include <iostream.h>

#include <fstream.h>

#include <math.h>

const double pi = 3.14;

const double OFFSET = 0.2;

int main() {

fstream fptr;

9

fptr.open("tmp.txt", fstream::out);

10

ac fixed<7,1,true,AC TRN,AC SAT> x[128];

11

12

for(int i=0; i<128; i++){

13

x[i] = OFFSET + 0.98*sin(2*pi*i/(double)64);

14

fptr << x[i] <<endl;</pre>

15

16

fptr.close();

17 }

```

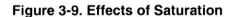

Figure 3-9 shows the results of adding saturation in Example 3-7.

Examination of Figure 3-9 shows that enabling saturation has prevented any overflow or under flow. However the figure also clearly shows that the waveform is non-linear. This non-linearity, also known as clipping, has

the effect of adding noise into the system. This is one of the main reasons why most algorithms should be designed without the use of saturation.

# Saturation should only be used when absolutely necessary. Most algorithms can be designed to avoid overflow/underflow by selecting the appropriate variable bit widths to support the full dynamic range of the algorithm. Saturation usually impacts both area and performance.

#### **Operators**

All of the standard C++ arithmetic and logical operators are supported by the ac\_int and ac\_fixed data types. The operators such as multiplication, addition, etc, are designed to return a result without a loss of precision. The Algorithmic C reference manual should be consulted for a full description of all operators. Operators such as divide "/" and modulus "%" are supported but should be used with care when the two operands are variables. This is because an operation such as division costs a great deal in area, and the reality is that most hardware designers would never use a hardware divider. This is often a misunderstood area of HLS since it is perfectly reasonable to write something like z = x/y in C++. If a divide is truly needed, there are cheaper implementations such as the CORDIC algorithm. Most HLS tools provide a library that implements these functions more efficiently. Divisions or modulus by a constant are much more acceptable, and are implemented using add and shift logic. Divide or modulus by a power of two is implemented using static shifts, and cost nothing in additional area. Two operators whose behavior is worth noting are the bit select and shift operators, but first a quick discussion of arithmetic operators.

#### Bitwise Arithmetic Operators: \*, +, -, /, &, |, ^,%

The Algorithmic C bitwise arithmetic operators are designed so that there is no loss of precision in the return value. Furthermore the mixture of signed and unsigned Algorithmic C data types is supported, and returns the expected signedness.

The return type of an arithmetic operation automatically takes care of bit growth so that there is no loss of precision. This can be done automatically because the bit widths of the two operands are specified as template parameters when the ac\_int variables are declared. This is shown below:

```

ac_int<8,true> a,b; //8-bits signed

```

Multiplying "a" times "b", each with 8 bits of precision, requires 16 bits of precision:

```

(returns ac int<16, true>) (a*c)

```

Adding "a" plus "b" requires nine bits of precision:

```

(returns ac_int<9,true>)(a+b)

```

#### Bit Select Operator: []

Individual bits can be read or written from an ac\_int or ac\_fixed data type using the [] operator. The operator index selects the bit position. E.g. x[1], x[3], x[7]. The return value is an object of class ac\_int::bitref and a built-in conversion function to ac\_int and bool are provided. The code fragment below shows how the bit select operator can be used to read the sign bit of an ac\_int.

```

ac_int<11,true> x;

bool is_neg;

if(x[10]) //test for sign bit treated as bool

is_neg = true;

else

is neg = false;

```

The bit select operator can just as easily be used to write a bit in an ac\_int or ac\_fixed. E.g.

```

ac_fixed<9,1,false> x = 0;

bool add_one = true;

if(add_one)

x[8] = 1; //set MSB of x

```

#### Shift Operators: <<, >>

The shift operators are worthy of discussion because, unlike the arithmetic operators which maintain full precision, they return the precision of the left operand. This can lead to unexpected results. Furthermore, designers should pay attention to how they use shifts because both operands can be signed or unsigned. This can also lead to surprising results that would not be possible in traditional RTL.

#### Shift Right Operator: >>

#### **Unsigned Shift Right**

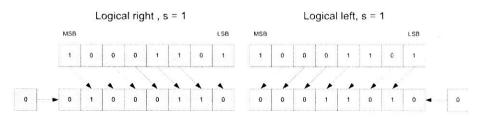

The unsigned right shift operator applied to unsigned ac\_int or ac\_fixed data types behaves exactly how an RTL designer would expect a shifter to behave. Each bit is shifted right by the shift amount and zeros are stuffed into the upper bits. This can best be seen by a graphical example shown in Figure 3-10. The variable being shifted is a 4-bit unsigned integer that is initialized with all bits set equal to 1. As the shift amount is increased zeros are stuffed into the MSBs.

```

ac_int<4,false> x = -1; //set all bits to 1's

int idx;

ac_int<4,false> y = x >> idx;

```

Figure 3-10. Unsigned Shift Right

|   | } | / |   | <u>idx</u> | Value of y |

|---|---|---|---|------------|------------|

| 1 | 1 | 1 | 1 | 0          | 15         |

| 0 | 1 |   |   | 1          | 7          |

| 0 | 0 | 1 | 1 | 2          | 3          |

| 0 | 0 | 0 | 1 | 3          | 1          |

| 0 | 0 | 0 | 0 | 4          | 0          |

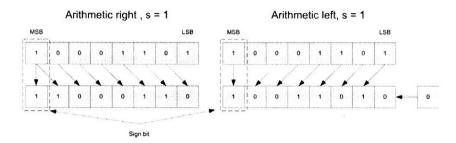

#### Signed Shift Right

Signed shift right has somewhat unexpected behavior. Most hardware engineers think of right and left shifts as either divides or multiplies by power of two. So one would expect that at some point right shifting sets

all bits to zero as was shown in Figure 3-10. However, when right shifting a signed ac\_int, the sign bit is always kept, which has the end result of shifting ones from the MSB rather than zeros. This is shown in Figure 3-11. The ac\_int "x" is initialized with the sign bit set equal to one and all other bits zero, which is equal to negative eight. Each increasing shift has the effect of dividing by increasing powers of two until all bits are set to one. From this point forward the result is always negative one.

```

ac_int<4,true> x = 0;

x[\overline{3}] = 1 //set x equal -8

int idx;

ac int<4,true> y = x >> idx;

```

Figure 3-11. Signed Right Shift

|   | , | / |   | <u>idx</u> | Value of y |

|---|---|---|---|------------|------------|

| 1 | 0 |   | 0 | 0          | -8         |

| 1 | 1 | 0 | 0 | 1          | -4         |

| 1 | 1 | 1 | 0 | 2          | -2         |

| 1 | 1 | 1 | 1 | 3          | -1         |

| 1 | 1 | 1 | 1 | 4          | -1         |

#### Shift Left Operator: <<

The left shift operator behaves mostly as one would expect, with the exception being when assigning to a variable with larger precision. The typical behavior is discussed first.

#### **Unsigned Shift Left**

Shifting an unsigned ac\_int left and assigning the result to a variable with the same precision has similar behavior as an unsigned shift right, except that zeros are stuffed from the LSB position, shown in Figure 3-12.

```

ac_int<4,false> x = -1; //set all bits to 1's

int idx;

ac_int<4,false> y = x << idx;</pre>

```

Figure 3-12. Unsigned Shift Left

|   | у |     | <u>idx</u> | Value of y |

|---|---|-----|------------|------------|

| 1 | 1 | 1 1 | 0          | 15         |

| 1 | 1 | 1 0 | 1          | 14         |

| 1 | 1 | 0 0 | 2          | 12         |

| 1 | 0 | 0 0 | 3          | 8          |

| 0 | 0 | 0 0 | 4          | 0          |

#### Signed Shift Left

Signed shift left has similar behavior to unsigned shift left where zeros are stuffed from the LSB.

```

ac_int<4,true> x = -1; //set all bits to 1's

int idx;

ac int<4,true> y = x << idx;</pre>

```

Figure 3-13. Signed Shift Left

|   | у |   |   | <u>idx</u> | Value of y |

|---|---|---|---|------------|------------|

| 1 | 1 | 1 | 1 | 0          | -1         |

| 1 | 1 | 1 | 0 | 1          | -2         |

| 1 | 1 | 0 | 0 | 2          | -4         |

| 1 | 0 | 0 |   | 3          | -8         |

| 0 | 0 | 0 | 0 | 4          | 0          |

#### **Unexpected Loss of Precision**

Shifting left can have unexpected, but correct, behavior when the expectation is that the result is based on the precision of the target variables. This is best understood by looking at an example:

```

ac_int<4,false> x = -1; //set all bits to 1's

int idx;

ac_int<8,false> y = x << idx;</pre>

```

In the example shown above, "x", which is four bits unsigned, is shifted left and assigned to "y", which is eight bits unsigned. A common

misconception by designers new to Algorithmic C data types is that the upper bits of "x" are stored in "y" as they are shifted past the MSB of "x". Figure 3-14 shows the actual behavior. Remember that the shift operator returns the precision of the left operand, which is four bits in this example. In order to preserve the bits that are being shifted out of the MSB of "x" it is necessary to cast "x" to the precision of "y". E.g.

```

ac_int<4,false> x = -1; //set all bits to 1's

int idx;

ac int<8,false> y = (ac int<8,false>) x << idx;</pre>

```

#### Note —

Shifting left can result in loss of bits if the variable being shifted is not cast to the same precision as the left hand of the assignment.

This now gives the desired behavior shown in Figure 3-15.

Figure 3-14. Unexpected Loss of Precision Shifting Left

|   |   |   |   | у |   |   |   | <u>idx</u> | Value of y |

|---|---|---|---|---|---|---|---|------------|------------|

| 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0          | 15         |

| 0 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 1          | 14         |

| 0 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 2          | 12         |

| 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 3          | 8          |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 4          | 0          |

Figure 3-15. Casting to Desired Precision Shifting Left

|   |   |   |   | у |   |   |   | <u>idx</u> | Value of y |

|---|---|---|---|---|---|---|---|------------|------------|

| 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0          | 15         |

| 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1          | 30         |

| 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 2          | 60         |

| 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 3          | 120        |

| 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 4          | 240        |

#### Methods

The Algorithmic C data types provide a number of built-in methods which are covered in detail in the reference manual. The methods most often used for design and simulation are covered below.

Slice Read: slc

The slice read method has the form: slc<W>(int lsb)

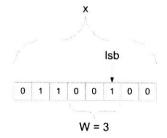

Where the template parameter "W" specifies the width of the slice, and "lsb" points to where the slice begins. Dynamic sizing of the slice width is not possible because "W" is a template parameter. However it is possible to dynamically change the value of "lsb". Consider the following example where a three bit slice is read from "x" and assigned to "y". "lsb" points to bit position two. Figure 3-16 shows graphically how the read slice works.

```

ac_int<8, false> x = 100;

ac_int<3, false> y;

y = x.slc<3>(2);

```

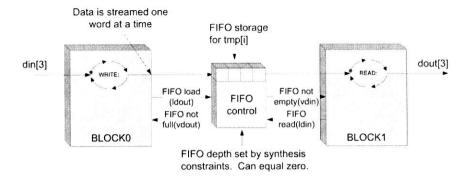

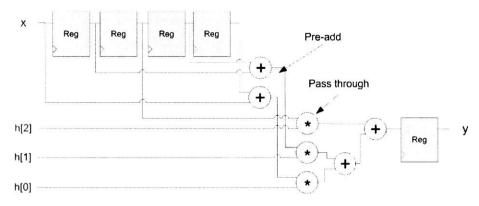

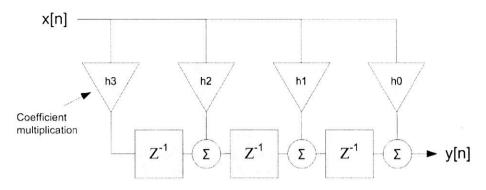

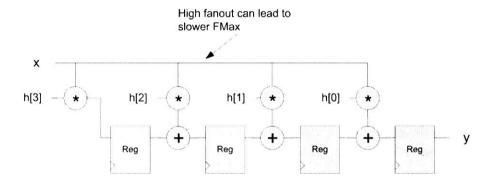

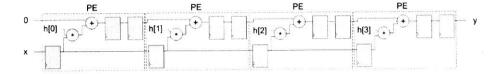

Figure 3-16. Read Slice